EXAMEN ARCHITECTURE DES ORDINATEURS TEST 18

Sujet d'examen CONVERSION, multplixeurs, logique combinatoire, boolr, bscule t, memoire, montage, led, table de verite 20pts

Exercice1 : Boolr 4PTS

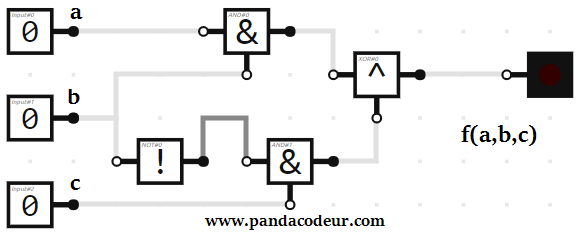

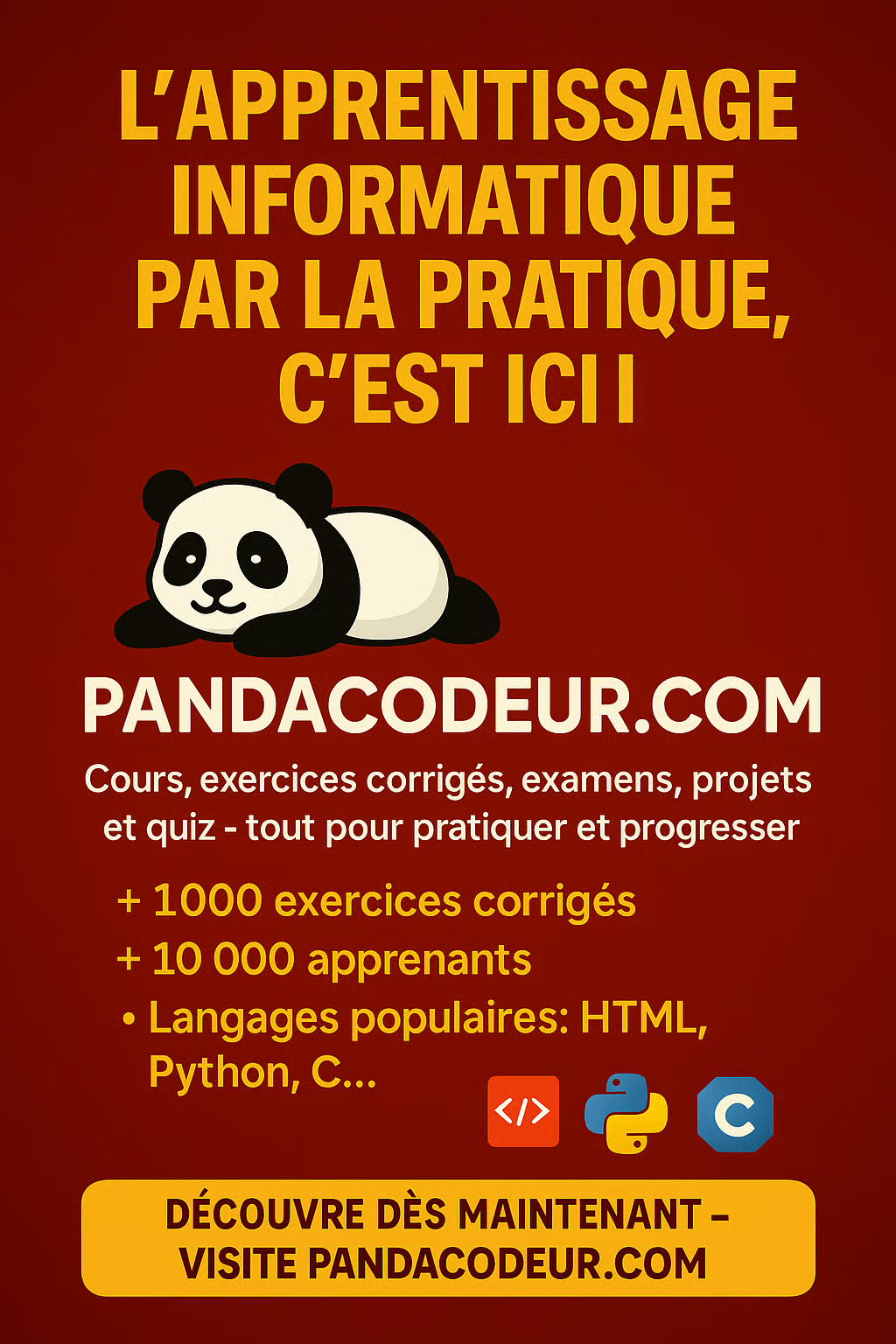

Soit le montage realiser avec le simulateur BOOLR :

- Donner l'equation logique de ce montage.

- Tracer la table de verite de ce montage puis donner la fonction f(a, b, c) de ce montage.

- Dans quelle situation la LED s'allume t-elle ?

- Donner le schema logique de ce circuit en utilisant des portes Americaine.

- Donner l'equation simplifie de cette fonction en forme normale Conjonctive.

Exercice 2 : Numeration 5PTS

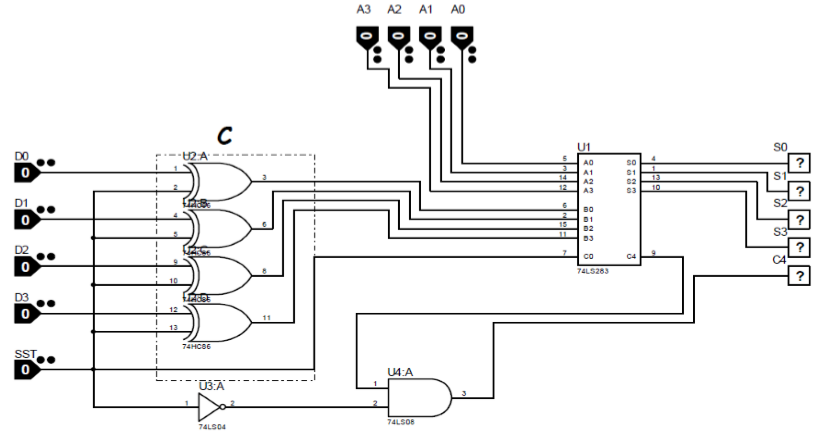

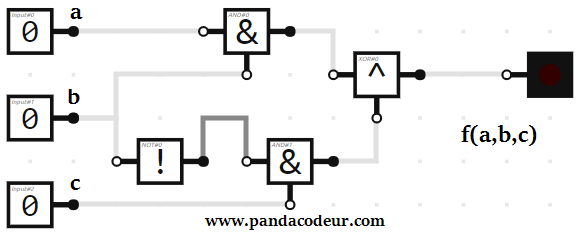

Soit le montage suivant qui représente un additionneur- soustracteur de deux nombres à 4 bits :

1) Demi-Soustracteur / Demi-Additionneur. Réaliser un demi-soustracteur / demi-Additionneur :

a) Ecrire la table de vérité.

b) Donner les équations de sortie.

c) Etablir le schéma logique.

2) Donner le rôle de l’entrée SST.

3) Donner le rôle du circuit C .

4) Le rôle de l'entree C0 et C4

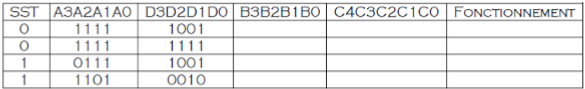

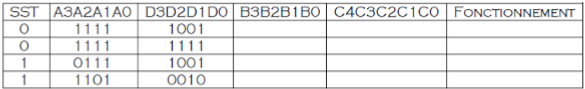

5) Compléter le tableau suivant :

Exercice 3 : Bascules 6PTS

Nous souhaitons construire un compteur réversible (décomptage) synchrone modolu 4. Nous utilisons deux entrée a et à pour définir le mode de fonctionnement.

|

Fonctionnement

|

|

a=0 b=0

|

0-1-2-3

|

|

a=1 b=0

|

0-2

|

|

a=0 b=1

|

0-3-2-1

|

|

a=1 b=1

|

2-0

|

a définit le pas de comptage a=0 le pas est 1 et a=1 le pas est 2. b définit le mode (comptage/décomptage), b = 0 on incremente le pas, b = 1 on décrémente le pas.

Un autre cas peut apparaitre : Par exemple a=1 et b=0 lorsque la valeur du compteur est 3, alors on incrémente de 2 modulo 4 on obtient 1. Si b=1 alors on décrémente du pas module 4 et on obticat encore 1. La table de vérité fera apparaitre tous ces cas. A ce circuit, nous ajoutons deux sorties pour déterminer le changement de parité. Ils s'agit des sorties s0 et s1 . La sortie s1 vaut 1 lorsqu'on compte d'un nombre pair pour un nombre impair et 0 sinon. La sortie s0 vaut 1 lorsqu'on compte d'un nombre impair pour un nombre pair et 0 sinon.

1. Combien de bascule sont nécessaires pour ce compteur réversible?

2. Dessinez le diagramme d'états transition. en précisant les valeurs des sorties.

3. Complétez la table de transition ci-contre, avec les valeurs des sorties ainsi que Ics entrées des bascules T, sachant que Q^{n+1}=T^{n}\oplus Q^{n}.

4. Déterminez les équations des sorties du circuit et des entrées des bascules (en fonction des entrées a et b ainsi que de l'état présent).

5. Dessinez le circuit logique.

Exercice 4 : 5pts Memoire

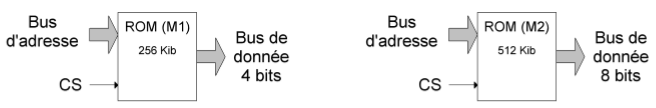

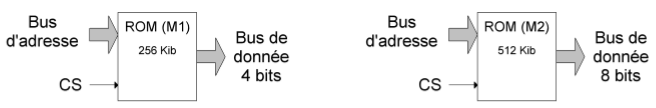

Soit les deux mémoires de type ROM suivantes :

1. Combien peut-on former de mots de 4 bits avec la mémoire M1 ?

2. Combien peut-on former de mots de 8 bits avec la mémoire M2 ?

3. Quelle est la taille du bus d’adresse des deux types de ROM ?

On souhaite réaliser une mémoire M2 à l’aide de deux mémoires M1.

4. Quel type d’assemblage doit-on réaliser ?

5. Donnez le schéma de câblage.