EXAMEN ARCHITECTURE DES ORDINATEURS TEST 27

Sujet d'examen CONVERSION, examen boolr, multplixeurs, logique combinatoire, boolr, bscule t, memoire, montage, led, table de verite 20pts

Exercice1 : Boolr 5PTS

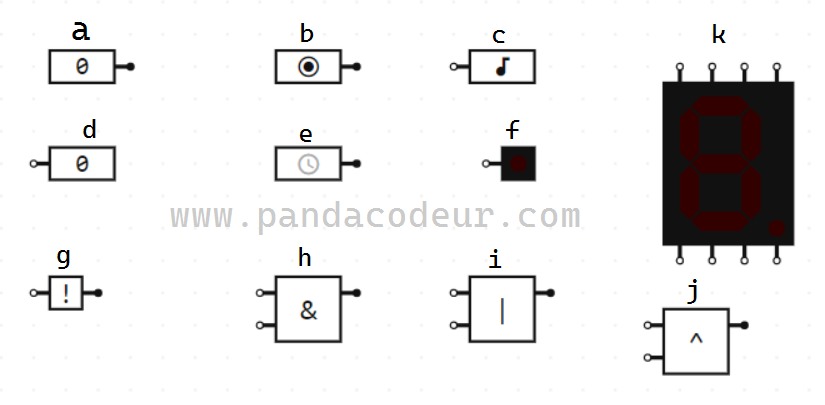

1) Donner nom/ rôle aux différents composants de boolr :

2) Quels sont les éléments qui peuvent etre reliés entre eux ?

2) Quels sont les éléments qui peuvent etre reliés entre eux ?

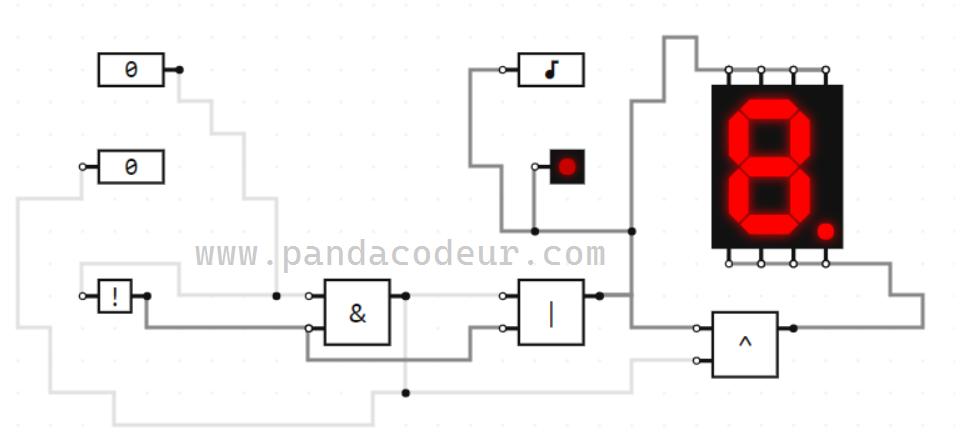

3) Donner une explication au schéma suivant :

Exercice 2 : /3PTS

Le compteur A est un compteur synchrone intégré modulo 5.

Le compteur B est un compteur synchrone intégré modulo 2.

Le compteur C est un compteur synchrone intégré modulo 3.

Utilisez ces trois circuits pour réaliser le circuit séquentiel d’un compteur BCD synchrone de 0 à 29.

Exercice 3 : Bascules 7PTS

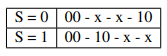

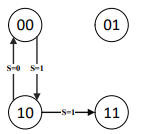

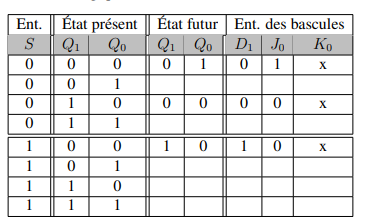

Nous souhaitons développer un compteur synchrone réversible modulo 4 afin de produire une séquence de code GRAY. Ce compteur réalise un comptage lorsque l’entrée S vaut 0 et un décomptage lorsque S vaut 1.

1) Complétez le tableau ci-dessus afin de produire une séquence de code GRAY.

2) Combien d’éléments de mémorisation possède ce compteur ?

3) Compléter le diagramme d’état ci-contre.

Nous utilisons une bascule D et une bascule JK.

(a) Rappelez les équations de transition des bascules D et JK.

(b) En utilisant le diagramme d’état et ces équations, complétez la table de transition ci-dessous.

(c) Déterminez les équations des entrées des bascules (en personne de 5 et de 7 cm présents).

(d) Dessinez le circuit logique.

Transitions

\( S = 0 \) \( 00 - x - x - 10 \)

\( S = 1 \) \( 00 - 10 - x - x \)

Exercice 4 : 5pts Memoire

À l’aide de plusieurs RAM (M1) de 512 octets possédant un bus de données de 4 bits, on souhaite réaliser une RAM (M2) de 8 Kio = 8 * 1024 octets possédant un bus de données de 16 bits.

- Donnez le nombre de mots et la largeur du bus d’adresse (nombre de bit d’adresse) pour les deux types de RAM (M1 et M2).

- Combien de mémoires M1 doit-on assembler en parallèle ? Faire le schéma et nommez la nouvelle mémoire M’.

- Combien de mémoires M1 doit-on assembler en série ? Faire le schéma et nommez la nouvelle mémoire M”.

- Combien de bits d’adresse vont servir à déterminer le CS des mémoires M1 ?

- En utilisant les mémoires M’, réalisez la table d’adressage pour la réalisation de la mémoire M2.

- Dessinez le schéma de câblage.